FORTH-ICS/TR-339

July 2004

# Design of a 32x32 Variable-Packet-Size Buffered Crossbar Switch Chip

Dimitrios G. Simos

#### Abstract

Switches and routers are the basic building blocks of most modern interconnections and of the Internet, aiming at providing datapath connectivity, while solving output contention, the major problem of distributed, multi-party communication. The latter is accomplished through buffering, access control, flow control, or datagram dropping. Modern high-end switches are called upon to provide aggregate throughputs in the terabit per-second range, which greatly challenges both their architecture and implementation technology.

The aim of this work is to prove the feasibility of a novel buffered crossbar organization, operating directly on variable-size packets. Such operation, combined with distributed scheduling, removes the need for internal speedup, thus fully utilizing the incoming throughput.

We proved the feasibility of this novel architecture by fully designing such a 32x32 buffered crossbar, in the form of an ASIC chip core, providing 300 *Gbit/sec* of aggregate bandwidth in 0.18  $\mu m$  technology, or higher throughput in more advanced technologies. The design was synthesized, placed, and routed, using a hierarchical ASIC flow, resulting in a 420  $mm^2$ , 6 Watt core in 0.18  $\mu m$  CMOS technology. In 0.13  $\mu m$  CMOS, area would be reduced to 200  $mm^2$ , and power consumption to 3.2 W. Power estimation showed that the majority of power is consumed in driving cross-chip wires, while memories and logic are minority consumers.

Hierarchical ASIC flows are difficult to use, but became necessary due to the large size of the design. We present the detailed system design (block diagrams as well as critical circuit details), followed by a detailed description of the design flow, including its numerous intricacies and the lessons that we learnt. In particular, we describe the choice of a hierarchy that is appropriate for effective placement, routing, and timing behavior. The final placement and routing showed that the synthesis tool had underestimated the design area by 30%, due to the dominance of long (end-to-end) wires in this design.

ii

# Design of a 32x32 Variable-Packet-Size Buffered Crossbar Switch Chip

Dimitrios G. Simos

Computer Architecture & VLSI Systems (CARV) Laboratory Institute of Computer Science (ICS) Foundation for Research and Technology – Hellas (FORTH) Science and Technology Park of Crete P.O. Box 1385, Heraklion, Crete, GR-711-10 Greece Tel.: +30-81-391660 Fax: +30-81-391661 email: simos@ics.forth.gr

# Technical Report FORTH-ICS/TR-339 – July 2004

Copyright 2004 by FORTH

Work performed as a M.Sc. Thesis at the Department of Computer Science, University of Crete, under the supervision of prof. Manolis Katevenis

#### Abstract

Switches and routers are the basic building blocks of most modern interconnections and of the Internet, aiming at providing datapath connectivity, while solving output contention, the major problem of distributed, multi-party communication. The latter is accomplished through buffering, access control, flow control, or datagram dropping. Modern high-end switches are called upon to provide aggregate throughputs in the terabit per-second range, which greatly challenges both their architecture and implementation technology.

The aim of this work is to prove the feasibility of a novel buffered crossbar organization, operating directly on variable-size packets. Such operation, combined with distributed scheduling, removes the need for internal speedup, thus fully utilizing the incoming throughput.

We proved the feasibility of this novel architecture by fully designing such a 32x32 buffered crossbar, in the form of an ASIC chip core, providing 300 *Gbit/sec* of aggregate bandwidth in 0.18  $\mu m$  technology, or higher throughput in more advanced technologies. The design was synthesized, placed, and routed, using a hierarchical ASIC flow, resulting in a 420  $mm^2$ , 6 Watt core in 0.18  $\mu m$  CMOS technology. In 0.13  $\mu m$  CMOS, area would be reduced to 200  $mm^2$ , and power

consumption to 3.2 W. Power estimation showed that the majority of power is consumed in driving cross-chip wires, while memories and logic are minority consumers.

Hierarchical ASIC flows are difficult to use, but became necessary due to the large size of the design. We present the detailed system design (block diagrams as well as critical circuit details), followed by a detailed description of the design flow, including its numerous intricacies and the lessons that we learnt. In particular, we describe the choice of a hierarchy that is appropriate for effective placement, routing, and timing behavior. The final placement and routing showed that the synthesis tool had underestimated the design area by 30%, due to the dominance of long (end-to-end) wires in this design.

# Acknowledgments

This work was performed at and financially supported by the Institute of Computer Science (ICS) of the Foundation for Research & Technology -Hellas (FORTH), Heraklion, Crete, Greece, partly through project 002075 "SIVSS" of the European Union FP6 IST Programme. The CAD tools were provided by the University of Crete, through Europractice.

Besides these organizations, I would also like to thank all those people who helped me throughout this work. First of all, I would like to thank my supervisor, prof. Manolis Katevenis for defining the chip architecture after originally observing that a buffered crossbar can operate directly on variablesize packets. Also, more importantly, his priceless suggestions on organizing and carrying out a project, and his simple yet scientific way of thinking and teaching, became valuable guides for me during the last few years. I deeply thank him for that.

I would also like to thank the rest of the Packet Switch Architecture group at ICS-FORTH for their help: Dr. Ioannis Papaefstathiou and prof. Dionysios Pnevmatikatos for their suggestions and observations on all the design stages of the chip –their experience in the development of large projects proved invaluable; Nikolaos Chrysos and Georgios Passas, for our conversations and their help during the last 2 years; Giorgos Kalokairinos for his support.

Also, I give my thanks to Dr. Christos Sotiriou for his suggestions on the back-end flow; Vassilis Papaefstathiou for our valuable hardware-oriented discussions during our breaks; and Michalis Ligerakis for his help.

I would also like to thank Dr. Ioannis Papaefstathiou, prof. Aggelos Bilas, Aggelos Ioannou, Nikolaos Chrysos, Olga Dokianaki, and Evriklis Kounalakis for their corrections on parts of this thesis report.

Thanks are also due to all my friends, especially to: Dimitris Zaharakis, Katerina Iskioupi, Thom Kleitsakis, Haris Kondylakis and Dimitris Christelis. Your support will never be forgotten.

I also thank my brothers, Panos and Vassilis, and, last but not least, my deepest thanks go to my parents, Giorgos and Sevasti, for their support all these years: nothing would have been accomplished without your contribution; I therefore dedicate this work to you.

vi

# Contents

| 1        | Intr               | roduction and Motivation                        | 1        |

|----------|--------------------|-------------------------------------------------|----------|

|          | 1.1                | Queueing Architectures                          | 1        |

|          | 1.2                | Related Work                                    | 6        |

|          |                    | 1.2.1 Unbuffered Crossbar Implementations       | 6        |

|          |                    | 1.2.2 Buffered Crossbar Implementations         | 7        |

|          | 1.3                | Contributions of this Work                      | 8        |

|          | 1.4                | Motivation: Large-Scale CICQ Switch Feasibility | 9        |

|          |                    | 1.4.1 Transistor sizes                          | 10       |

|          |                    | 1.4.2 On-Chip Memory $\ldots$                   | 10       |

|          |                    | 1.4.3 Chip/Wafer Sizes $\ldots$                 | 11       |

|          |                    | 1.4.4 Power Consumption                         | 11       |

| 0        | а.                 |                                                 | 10       |

| <b>2</b> |                    | 8                                               | 12       |

|          | 2.1                |                                                 | 12       |

|          | 2.2                |                                                 | 12       |

|          |                    | 1 ( 1 /                                         | 14       |

|          |                    | 1                                               | 17       |

|          |                    |                                                 | 19       |

|          | 0.0                | 0                                               | 22       |

|          | 2.3                | Conclusions                                     | 24       |

| 3        | Log                | cic Synthesis                                   | 25       |

|          | 3.1                | Introduction                                    | 25       |

|          | 3.2                | Synthesis Flow                                  | 25       |

|          | 3.3                | *                                               | 26       |

|          | 3.4                |                                                 | 28       |

|          | 3.5                |                                                 | 29       |

| 4        | Dla                | compart and Douting                             | 31       |

| 4        | <b>F</b> 1a<br>4.1 |                                                 | -        |

|          | $4.1 \\ 4.2$       | 0                                               | 31<br>22 |

|          | 4.2<br>4.3         | 0 0                                             | 33<br>35 |

|          |                    | 8                                               |          |

|          | 4.4                | 8                                               | 38       |

|          | 4.5                | Credit Scheduler Placement and Routing          | 38       |

|              | 4.6 | Adding Another Level of Hierarchy: Top Level Placement and              |    |

|--------------|-----|-------------------------------------------------------------------------|----|

|              |     | Routing                                                                 | 39 |

|              | 4.7 | Chip Packaging and Placement and Routing Results                        | 41 |

|              |     | 4.7.1 Chip Packaging                                                    | 41 |

|              |     | 4.7.2 P&R Results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 43 |

|              | 4.8 | Conclusions: Dealing With Large and Regular Designs                     | 44 |

| <b>5</b>     | Pow | er Consumption                                                          | 46 |

|              | 5.1 | Crossbar Switch Power Consumption Estimation: Work Done                 |    |

|              |     | Sofar                                                                   | 48 |

|              | 5.2 | Power Analysis Flow: RTL vs. Gate Level vs. Post-P&R                    | 49 |

|              |     | 5.2.1 Gate Level Power Estimation                                       | 50 |

|              |     | 5.2.2 Post-P&R Power Estimation                                         | 51 |

|              | 5.3 | Switch Power Consumption Breakdown                                      | 52 |

|              | 5.4 | Conclusions                                                             | 54 |

| 6            | Con | clusions and Future Work                                                | 56 |

|              |     |                                                                         |    |

| Α            | 0   | anization of a 4-input WRR Scheduler                                    | 58 |

|              | A.1 | 0                                                                       | 58 |

|              |     | Weighted Round Robin Scheduling                                         | 59 |

|              | A.3 | 4×4 Output Scheduler Organization                                       | 60 |

|              | A.4 | WRR Output Scheduler Implementation                                     | 62 |

| В            | Pow | er Estimation Tutorial                                                  | 64 |

|              | B.1 |                                                                         | 64 |

|              | B.2 | Post-P&R Level Power Estimation                                         | 66 |

| $\mathbf{C}$ | Cad | ence Encounter Tutorial and Scripts                                     | 67 |

|              | C.1 | Setting the Environment                                                 | 67 |

|              | C.2 | Placement & Routing Stages                                              | 68 |

|              |     | C.2.1 Design Import                                                     | 68 |

|              |     | C.2.2 Floorplaning & Pin Assignment                                     | 68 |

|              |     | C.2.3 Medium Effort Placement                                           | 70 |

|              |     | C.2.4 Trial Routing                                                     | 71 |

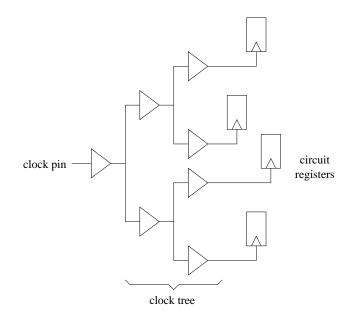

|              |     | C.2.5 Clock Tree Synthesis                                              | 73 |

|              |     | C.2.6 Timing Driven Placement                                           | 75 |

|              |     | C.2.7 Timing Driven Final and Global Route                              | 75 |

|              |     | C.2.8 Timing Reports and Design Optimizations                           | 77 |

| D            | Swi | tch Synchronization Details                                             | 80 |

|              | D.1 | Introduction                                                            | 80 |

|              | D.2 | The Metastability Problem                                               | 80 |

|              | D.3 | Synchronizer Requirements                                               | 82 |

|              | D.4 | 1-bit Synchronizer Design                                               | 83 |

| $\mathbf{E}$ | Pow | ver Optimization Techniques                     | 84 |

|--------------|-----|-------------------------------------------------|----|

|              | E.1 | RTL Power Optimization                          | 84 |

|              |     | E.1.1 Glitch Minimization                       | 84 |

|              |     | E.1.2 Exploitation of Resource Sharing          | 85 |

|              |     | E.1.3 Dynamic Power Management                  | 86 |

|              | E.2 | Gate Level Power Optimization                   | 88 |

|              |     | E.2.1 Technology-independent Techniques         | 88 |

|              |     | E.2.2 Technology-dependent Techniques           | 89 |

| $\mathbf{F}$ | LFS | R Random Number Generators                      | 93 |

|              | F.1 | Traffic Analysis                                | 93 |

|              |     | Hardware Random Number Generators               |    |

|              | F.3 | Non-uniform Number Hardware Sequence Generation | 96 |

| G            | The | esis Overview                                   | 97 |

# List of Figures

| 1.1  | Conceptual Derivation & Taxonomy of Queueing Architectures 2 |

|------|--------------------------------------------------------------|

| 1.2  | Output Queueing Architecture                                 |

| 1.3  | Input Queueing Architecture                                  |

| 1.4  | Combined Input Output Queueing or Internal Speedup Archi-    |

|      | tecture                                                      |

| 1.5  | Combined Input Crosspoint Queueing (CICQ) Architecture $6$   |

| 2.1  | $32 \times 32$ Crossbar Switch Block Diagram                 |

| 2.2  | Supported Packet Format                                      |

| 2.3  | Crosspoint Block Diagram                                     |

| 2.4  | Crosspoint Organization                                      |

| 2.5  | 1-bit Synchronizer Circuit                                   |

| 2.6  | RR Output Scheduler Block Diagram                            |

| 2.7  | RR Output Scheduler Organization                             |

| 2.8  | Credit Format                                                |

| 2.9  | RR Credit Scheduler Block Diagram                            |

| 2.10 | RR Credit Scheduler Organization                             |

| 2.11 | Line Card Block Diagram                                      |

| 2.12 | Line Card Packet Transmission FSM                            |

| 3.1  | Generic Synthesis Flow                                       |

| 3.2  | Synthesis Hierarchy Organization                             |

| 4.1  | Routing Global Wires in Hierarchical Designs                 |

| 4.2  | Switch Internal Organization: Block Interfaces               |

| 4.3  | Column Orientation Alternatives                              |

| 4.4  | Memory Layout                                                |

| 4.5  | Placement and Routing Flow                                   |

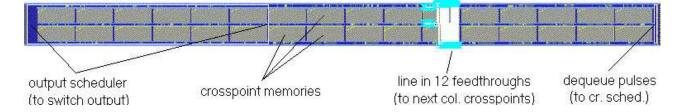

| 4.6  | Final Crosspoint Column Layout                               |

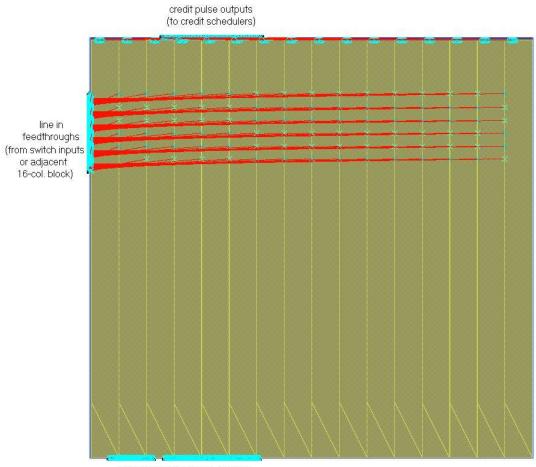

| 4.7  | 16-column Higher Level P&R                                   |

| 4.8  | Final Switch Core Layout 41                                  |

| 4.9  | Wire Bond and Flip Chip BGA Packaging Solutions 42           |

| 5.1  | Dynamic Power is Dissipated Even If the Output does not      |

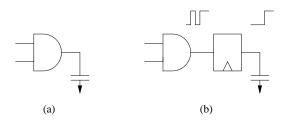

|      | Change                                                       |

| 5.2  | Components of Power Dissipation                              |

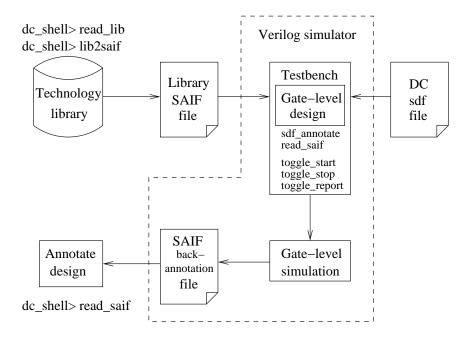

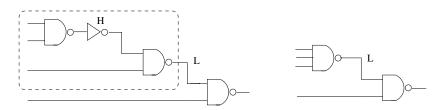

| $5.3 \\ 5.4$ | General Gate Level Power Estimation Flow Power Consumption Breakdown of the 32x32 Buffered Cross- | 51       |

|--------------|---------------------------------------------------------------------------------------------------|----------|

|              | bar Switch                                                                                        | 52       |

| 5.5          | Power Consumption Percentage Breakdown of the 32×32 Buffered<br>Crossbar Switch                   | ł<br>52  |

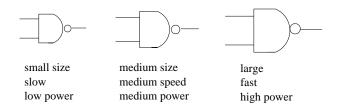

| 5.6          | Buffering of Long Input Lines.                                                                    | 52<br>53 |

| 5.7          | Module Power Activity in Worst-Case Steady-state Operation                                        | 54       |

| A.1          | Priority Queue WRR Scheduling Example                                                             | 60       |

| A.2          | 4-Input WRR Output Scheduler Block Diagram                                                        | 60       |

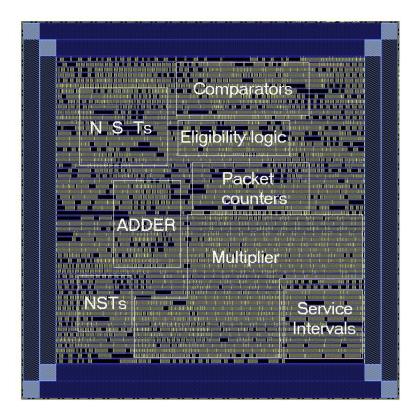

| A.3          | WRR Output Scheduler Internal Organization                                                        | 62       |

| A.4          | WRR Output Scheduler Chip Layout                                                                  | 63       |

| B.1          | Power Savings vs. Power Estimation per Design Level                                               | 64       |

| B.2          | Detailed Gate-Level Power Estimation Flow                                                         | 66       |

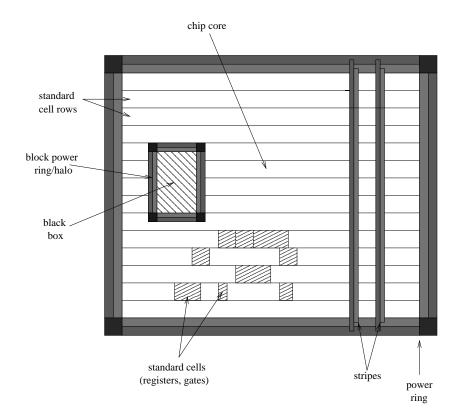

| C.1          | Chip Overview                                                                                     | 69       |

| C.2          | Clock Tree Example                                                                                | 74       |

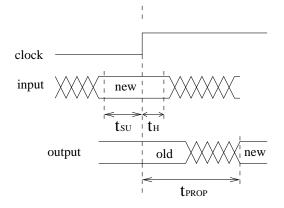

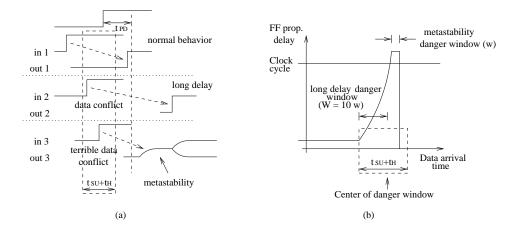

| D.1          | The Problem of Communicating Across Clock Domains                                                 | 80       |

| D.2          | Flip-Flop Timing Specification                                                                    | 81       |

| D.3          | Long Delay and Metastability Due to Data Conflicts                                                | 81       |

| D.4          | The 2 Flip-Flop Synchronizer                                                                      | 83       |

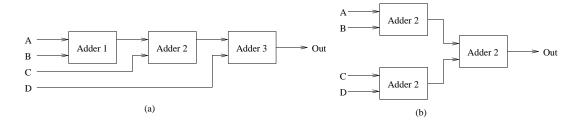

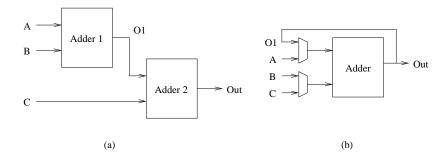

| E.1          | Path Balancing and Depth Reduction Power Optimization                                             | 85       |

| E.2          | Exploitation of Resource Sharing Power Optimization                                               | 85       |

| E.3<br>E.4   | Pre-computation Power Optimization                                                                | 86<br>87 |

| E.5          | State Assignment Power Optimization                                                               | 88       |

| E.6          | FSM Decomposition Power Optimization                                                              | 89       |

| E.7          | Retiming Power Optimization                                                                       | 90       |

| E.8          | Technology Mapping Power Optimization                                                             | 90       |

|              | Technology Library Primitive Characteristics                                                      | 91       |

|              | Buffer Insertion Power Optimization                                                               | 91       |

| E.11         | Dual-voltage Gate Power Optimization                                                              | 92       |

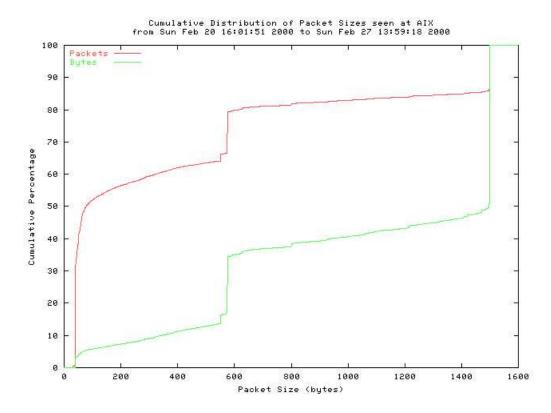

| F.1          | IP Packet Length Distribution                                                                     | 94       |

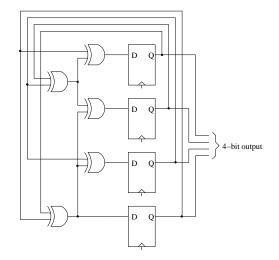

| F.2          | 4-bit Leap-forward Linear Feedback Shift Register (LFSR) Or-                                      | 05       |

|              | ganization                                                                                        | 95       |

| G.1          | Project Timeline                                                                                  | 97       |

# List of Tables

| 3.1 | Synthesis Results                       | 29 |

|-----|-----------------------------------------|----|

| 3.2 | Per Input/Output/Crosspoint Logic Costs | 30 |

| 4.1 | Placement and Routing Results           | 43 |

| G.1 | Thesis Code Size                        | 97 |

# Chapter 1 Introduction and Motivation

One important feature of crosspoint queued switches, which had not received much attention until recently, is the ability to route *directly* variable size packets, without the need to segment them at the ingress and reassemble them at the egress; this feature, combined with other crosspoint queueing advantages, allowed us to design a fairly large  $(32\times32)$  buffered crossbar switch operating at nearly 10 *Gbit/sec* link speeds, with no internal speedup. The design was synthesized and placed and routed by following a standard hierarchical ASIC flow, which resulted in a 420  $mm^2$ , 6 Watt chip in a 0.18 $\mu m$ technology. In this chapter we briefly present the most important Output Queueing architectures, along with their corresponding advantages and disadvantages. We introduce Crosspoint Queueing and we present previous work carried out in this field. Finally, we show roadmaps for current and future technologies which prove that large-scale crosspoint queueing will soon overcome its main drawback sofar, memory complexity.

# 1.1 Queueing Architectures

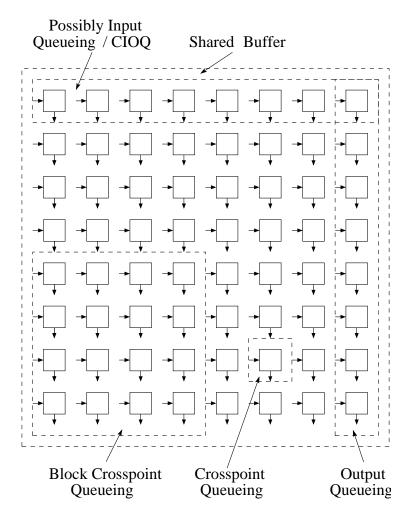

In order to introduce the reader to buffered crosspoint queueing, we first have to look into the various queueing architectures that have emerged up to now. Single-stage switches can be classified by their switching fabric and buffer architectures. The switching fabric is the physical connection within a switch between the input and output ports; it can be proved that all switches need a crossbar inside their switching fabric [1]. Usually packets need to be queued in buffers when short-term overloading occurs, where the sum of input rates for a single output port exceeds the outgoing link rate; hence, buffering characterizes all kinds of switches. In Figure 1.1 we can see a conceptual derivation and taxonomy of all types of queueing architectures, namely "Output Queueing (OQ)", "Input Queueing (IQ)", "Combined Input Output Queueing (CIOQ - Internal Speedup)", "Shared Buffer", "Block Crosspoint Queueing" and "Crosspoint Queueing (CQ)"; all architectures presented in this figure are being demonstrated on a  $8 \times 8$  switch - 8 inputs and 8 outputs. In this introductory section, we will analyze OQ, IQ, CIOQ, CQ, and the not-illustrated combination of "Combined Input Crosspoint Queueing (CICQ)".

Figure 1.1: Conceptual derivation & taxonomy of Queueing Architectures.

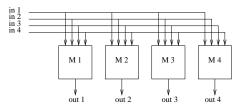

Traditional OQ is depicted in Figure 1.2. It is the reference switch architecture, as it is capable of delivering the best possible performance achievable; this stems from the fact that, in the absense of head-of-line (HOL) blocking at the ingress and internal blocking, minimum delay is guaranteed. HOL blocking occurs when a packet at the head of a queue that is destined to a congested output has to wait and possibly block other packets destined to uncongested outputs. Unfortunately, this "ideal" architecture is infeasible in the case of medium-to-large switch sizes and high link speeds, as it requires large memory throughput, hence it is expensive, or even not implementable: for a N port OQ switch, the buffer memory must operate N times the link speed in order to avoid packet loss; this event can happen when all input ports transfer packets to a single output port <sup>1</sup>. This "hot-spot" case occurs very often in client/server applications, where a popular server is connected to a single switch port and client requests arrive to the other N - 1 ports [2]. This speedup problem, combined with the fact that link speeds are increasing much faster than memory speeds, makes pure OQ architecture infeasible for gigabit rate networks. Furthermore, another disadvantage of the OQ architecture is the inefficiency of the buffer space partitioning: some memories may remain "almost" empty, whereas others might be "almost" full, although we have "paid" much in memory. This feature characterizes all switch architectures, apart from the Shared Buffer one.

Figure 1.2: Output Queueing (OQ) architecture: a  $4 \times 4$ -switch example is illustrated.

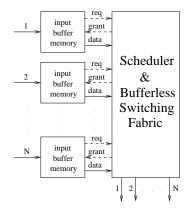

Input Queueing (IQ - see Figure 1.3) uses buffers at the ingress to store incoming data. These buffers must have a constant throughput of 2, and can have a single queue, or multiple queues; in the latter case the architecture is called "Advanced Input Queueing" or "Virtual Output Queueing". IQ switches with a single queue per input were studied and shown by Karol et al. [4] to have a limiting throughput of around 60% of their incoming throughput for Bernoulli packet arrivals with uniformly selected output ports. This limited throughput is due to HOL blocking at the input queues. There are two solutions to this problem: speedup the switching fabric <sup>2</sup>, or implement Virtual Output Queues (VOQs) at the ingress line cards; the latter solution has proved to be the most feasible one; as a result, most architectures based on IQ are of the VOQ-IQ style.

Unfortunately, if an unbuffered crossbar is used as the switching fabric of a VOQ-IQ switch: (a) synchronous operation is imposed; and (b) crossbar schedulers are inefficient, as it is hard to implement high throughput global schedulers. Synchronous operation has the result that: (i) variable-size packets have to be segmented into fixed-size cells before entering the crossbar and then reassembled at the egress; (ii) all cells have to be synchronized to a common internal clock, thus expensive synchronization circuits have to be used.

<sup>&</sup>lt;sup>1</sup>Consider, for example the case when all inputs wish to write to the same output: in the OQ example presented in Figure 1.2, memories must have write throughput of 4 and read throughput of 1; note that if we economize on write throughput, like "Knock-Out" architecture [3] does, then we risk to have to drop some packets on some situations.

<sup>&</sup>lt;sup>2</sup>Later on we will see that fabric speedup in IQ switches is needed for scheduling reasons, as well.

Furthermore, crossbar schedulers: (i) find it difficult to operate in very short cell times, as they cannot offer both high throughput and low latency; and (ii) it is hard to offer weighted fair queueing (WFQ) QoS [1]. Scheduling in VOQ-IQ switches is difficult because matching scheduling algorithms require complete "knowledge" of the input-to-output port head-of-line transmission requests <sup>3</sup>.

Figure 1.3: Input Queueing (IQ) architecture.

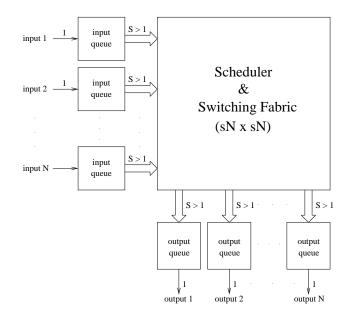

These problems can be overcome in two ways: (a) by using internal speedup and a traditional unbuffered crossbar switching fabric; and (b) by using a buffered crossbar as the switching fabric, but with no (or little) need for speedup. In the case that the switching fabric and schedulers are run at a higher speed, we have the Interal Speedup or Combined Input Output Queueing (CIOQ) switch (see Figure 1.4). Notice that most of the times the buffers at the ingress will be almost empty, while the ones at the egress almost full. Memory throughput still remains constant (1 + s, where s is the speedup factor), but this speedup factor, usually two to three in commercial products, actually limits the line rate, compared to the case when another architecture that did not require speedup was used instead.

The other solution is to add buffers to the crosspoints (shown in Figure 1.5); this organization is called Combined Input Crosspoint Queueing (CICQ). By this organization, information entering on different inputs can be destined to any output, as it does not have to be delivered to that output right away; it can be buffered to the corresponding crosspoint buffer instead. As a result, scheduling decisions need not be correlated to each other. Hence, no central scheduler is needed: input transmissions are independent of each other and independent of output transmissions. The  $N^2$  buffers needed in the case of a  $N \times N$  switch cannot be too large, due to implementation infeasibility. Instead, small buffers can be used, "backed up" by larger ones at

$<sup>^{3}</sup>$ Two of the most well known such scheduling algorithms are Parallel Iterated Matching (PIM) by Anderson et al. [13] and iterated SLIP (*i*SLIP) by McKeown [12].

Figure 1.4: Combined Input Output Queueing (CIOQ) or Internal Speedup architecture: speedup factor is s.

the input line cards, in a VOQ organization. Backpressure ensures that no crosspoint buffer will overflow.

Due to the fact that the schedulers operate independent of each other, no synchronized decisions are imposed; hence fixed-size cell operation and synchronization to a common clock are not needed any more. Furthermore, the loosely-coupled input and output schedulers, although not solving the matching problem in a short-term way <sup>4</sup>, can find very efficient long-term solutions to the crossbar scheduling problem, and are capable of offering advanced QoS, without the need for speedup. Egress buffering is also not needed, because no packet reassembly is required and no output queue can be built up, as there is no internal speedup.

To summarize, by adopting the CICQ architecture: (a) scheduling is simplified; (b) there is no need to mutually synchronize the line cards and to segment and reassemble packets, as *direct operation on variable-size packets is trivially supported*; (c) no internal speedup is required; and (d) very little (or no) memory is needed at the egress.

The major drawback of the CICQ architecture is the need to partition the switching fabric memory into  $N^2$  (in the  $N \times N$  case) buffers that must be located at the crosspoints. This characteristic prevented designers from adopting this organization in the case of medium- or large-scale switch solutions. In a later section we show that sub-micron technology transistor downscaling and new memory technologies have eliminated this drawback.

As a conclusion, provided that an Advanced Input Queued (VOQ) switch

$<sup>^4\</sup>mathrm{As}$  an unbuffered cross bar would do.

Figure 1.5: Combined Input Crosspoint Queueing (CICQ) architecture: small buffers at each crosspoint are "backed-up" by larger VOQs at the ingress line cards.

had a buffered crossbar as its switching fabric, scheduling would be simpler and packets would not have to be segmented and reassebled; as a result, no speedup would be necessary. In this work, we design, simulate, synthesize and place and route such a (medium-scale) buffered crossbar switch, and demonstrate its feasibility.

# 1.2 Related Work

In this subsection we present the most important unbuffered and buffered crossbar switch implementations that have emerged during the last few years. The aim is to show the progress that has taken place in this field, as well as highlight the special characteristics of our switch architecture.

#### 1.2.1 Unbuffered Crossbar Implementations

Various researchers have designed and implemented unbuffered crossbar switches in the past.

Heer et al. [16] "Self-routing Crossbar Switch" was a 12 port, 2 *Gbit/sec* per-port unbuffered switch implementation, running internally at 125 MHz and consuming 2.5 W of power. The overal area of the pad-limited design was 64  $mm^2$ , whereas the core area for the switching matrix, control logic and memories was about 25  $mm^2$  in a Siemens 0.25  $\mu m$  tecnology.

McKeown et al. designed a 320 *Gbit/sec*, fixed-size packet, input queued switch, with an unbuffered crossbar switching fabric and a sophisticated scheduler, back in 1996, called "Tiny Tera" [11]. The switch had 32 input

ports, operated at almost 10 Gbit/sec link speeds, distinguished 4 classes of service and efficiently supported multicast traffic. The switch did not suffer from HOL blocking, due to the use of Virtual Output Queues at the input buffers, whereas the scheduling algorithm was *i*SLIP [12]. The crossbar switch comprised of 1-bit crossbar slices and packets were segmented and sent through the crossbar in 64-bit chunks.

#### **1.2.2** Buffered Crossbar Implementations

Yoshigoe and Christensen simulated the idea of a "Parallel-Polled Virtual Output Queued (PP-VOQ)" buffered crossbar switch [14], with crosspoint memories of 1500 Bytes. The simulations, although of great value, did not take into account: (a) small/large RTT values; and (b) complicated and realistic enough traffic patterns. The same authors also proved the feasibility of a 24-port 10 Gbit/sec per-port FPGA implementation of a crossbar switch [15]. The input and output scheduling was plain Round-Robin, but by the use of a new Round-Robin Poller design. Target technology was the Xilinx [9] Virtex II series of FPGAs. The overall design was placed on a bus motherboard, with 6 line cards and one crossbar card attached to it. The crossbar card consisted of four crossbar slices, each of which communicated with the line cards, via the motherboard, through 24 "Rocket I/O" [10] tranceivers (3.125 Gbit/sec each). Memory and VOQ datapath was 16 bits wide and crosspoint buffer occupancy was transmitted over a dedicated parallel interface from the crosspoints to the line cards. The autors also implied that larger switches would be feasible in the future, due to larger amount of fast I/O circuits present in modern FPGAs. The switch did not support direct routing of variable-size packets, which was implied in [14].

Kariniemi et. al. [17] developed a  $4 \times 4$ , 5 *Gbit/sec* ATM buffered crossbar switch on an FPGA, for cable TV backbone networks. Internal SRAMs varied in size, from 32 to one KByte, due to the various ATM rates supported, with a total memory size of 1.12 Mbits.

One of the most important buffered crossbar implementations came from IBM Zurich [18]. It was a 4 *Tbit/sec* incoming throughput switching fabric (but 2.5 *Tbit/sec* incoming throughput switch), single-stage, combined input (with VOQs) and crosspoint queued (CICQ) switch, that supported long Round Trip Times (RTT), with line rates of 10 to 40 *Gbit/sec* (OC-192 to OC-768). Owing to the size of the switching fabric and the number of line cards, the switch was distributed over multiple racks, which could be as far as hundreds of feet apart; totally, 40 switching fabric and 64 interface chips were used. The switch supported 8 classes of service (priorities), but data entering the switch was still segmented into fixed-size packets of 64 or 80 Bytes, resulting in a line rate speedup of 1.6, in order to compensate for the switch packet header and segmentation overhead (hence the 4 *Tbit/sec* and 2.5 *Tbit/sec* difference). The chips were used. RTT supported could

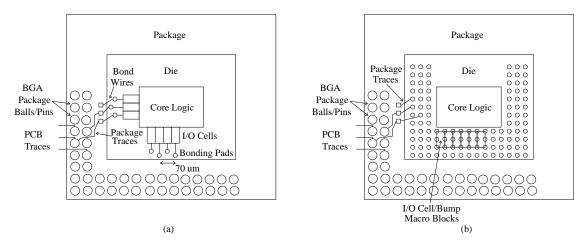

be as large as 64 packet cycles between the line cards and the switch core, and each crosspoint memory was  $2 \times RTT$  large, supporting both unicast and multicast traffic, which translated into at least 8 KBytes each. The same authors also stated that a die size of 250  $mm^2$ , a pin count of 1000 signal I/Os (totally 1500-pin package), and a single-chip power consumption of under 25 W are cost-effective borders for current state-of-the-art CMOS technologies <sup>5</sup>.

Today, FPGA vendors provide buffered crossbar switch solutions based on their latest FPGA models and I/O protocols, such as Altera [5] [6] and Xilinx [7] [8]. Such switch proposals however, lack scalability and enable designers to develop switches of sizes up to  $16 \times 16$ ; larger switches can be built by slicing the datapath to more than one FPGAs. Needless to say, the bottleneck in this case is the large  $(O(N^2))$  memory overhead, which inherently characterizes the buffered crossbar architecture.

Katevenis et al. [19] designed and simulated various speedup-less buffered crossbar sizes operating *directly* on variable-size packets, under complex and realistic Internet backbone traffic patterns and under different Round Trip Time (RTT) values <sup>6</sup>. The results showed that a crosspoint buffer size of *MaximumPacketSize* + *RTT* × *LineRate* is sufficient in order to achieve full output utilization <sup>7</sup>. Also, the organization proposed outperformed most *iSLIP*-based unbuffered switches, with speedup factors up to 2, and performed very close to the ideal OQ architecture, both in delay and throughput terms.

### **1.3** Contributions of this Work

The major contributions of the project within which this work was performed are: (a) to the best of our knowledge, it is the first ASIC core design of a buffered crossbar switch *directly* supporting variable-size packets; (b) the switch supports quite long RTT values efficiently; and (c) our performance is closer to ideal Output Queueing than that of alternative current designs, as proved in [19]. The contribution of this thesis is the design of the ASIC core, from block diagram level, through RTL description, synthesis, placement, routing, timing optimization, verification, and power estimation. The purpose of this thesis was to prove the feasibility of *single-chip* buffered crossbar switch designs in current and future CMOS technologies. In this thesis we describe the internal organization of the switch chip, showing its simplicity. Furthemore, we present the exact synthesis, placement and routing, power

<sup>&</sup>lt;sup>5</sup>These figures were taken into account in our buffered crossbar switch, too: the  $32 \times 32$  buffered crossbar switch designed in this work has an extrapolated area of 190  $mm^2$  and consumes 26.2 W in a 0.13  $\mu m$  technology.

<sup>&</sup>lt;sup>6</sup>Traffic generation is analyzed in detail in [29].

<sup>&</sup>lt;sup>7</sup>For example, for a 1500 Byte maximum packet size (TCP/IP), 10 *Gbit/sec* link speed and 400 nsec RTT, crosspoint buffer must be 2 KBytes.

estimation, and timing optimization flows based on the available tools, followed by fairly detailed tutorials; lastly, we provide guidelines which should be kept in mind when designing very large chips, such as design partitioning, hierarchy organization, important synthesis advices and place & route common problems and solutions.

# 1.4 Motivation: Large-Scale CICQ Switch Feasibility

As mentioned earlier, the result of this work was the ASIC-flow implementation of a  $32 \times 32$  buffered crossbar switch, supporting directly variable-packetsizes, and resulted in a  $420mm^2$ , 6 Watt chip in a  $0.18\mu m$  technology. This proves the feasibility of the concept: using a non-state-of-the-art technology  $(0.18\mu m)$ , a single-chip, multiport  $(32 \times 32)$  switch can be designed and implemented today. There are, however, two points worth mentioning: (a) the area is so large, that fabrication will only be possible with the largest wafer available today and yield will probably be unacceptably low; (b) the switch can handle easily today's traffic protocols (10/100 Mbps Ethernet packet sizes, that is, up to 1500 Bytes), but with "only" 2 KBytes of embedded SRAM per crosspoint, it lacks sufficient support for Gigabit Ethernet. Note that Fast Ethernet (100 Mbps) is currently the most used Ethernet standard, but Gigabit Ethernet is also starting to be used in backbone networks and 10 Gbps Ethernet is also emerging. Both support very large packet sizes, called "Jumboframes", with length of up to 9 KBytes.

In order to support such long packet sizes, without segementation and reassembly, each crosspoint memory would have to be approximately 10 KBytes. Traditional SRAMs of such size have an area density of  $12mm^2$  per Mbit[31], resulting in memory requirements of around  $1.1mm^2$  for each such memory! To make matters worse, such large on-chip SRAMs have approximately  $0.3 \ mW/MHz$  power consumption, resulting in 90mW for each of them and 2.9 Watts for the average worst-case scenario of a  $32 \times 32$  switch, where 32 memories are active all the time <sup>8</sup>; the respective values for 2 KByte SRAMs are  $0.28mm^2$ , 33 mW per-memory and 1W worst case power consuption.

As a result, feasibility of multiport switches, supporting future bottomlayer protocols and technologies is a very important issue. In this section we will examine various ways to overcome area limitations, by adopting emerging memory technologies. Transistor and chip sizes, as well as chip power consumption are also taken into account in this technology roadmap analysis. The latter seems to be another bottleneck in current and future ASIC designs, as it determines chip performance and, most importantly, its cost.

$<sup>^{8}</sup>$ In section 5.3 we explain why this is the worst-case typical-operation scenario.

#### 1.4.1 Transistor sizes

Transistor sizing has been improving for the past 30 years according to the "Moore's Law", which states that transistor density is doubling every 15-20 months. Although this law is somewhat philosophical and has changed a little bit since it first appeared by Gordon Moore, it still remains the main source for roadmap analyses, one of which appeares in [36].

Transistor down-sizing affects technology size, which is 90 nm today and will fall to 65 nm by 2007 and 45 nm by 2010 <sup>9</sup>. The above roadmap actually implies that logic becomes denser and denser, which means smaller chips. Technology downscaling will allow densities of 220  $MTransistors/cm^2$  at 80 nm (2005) to 450  $MTransistors/cm^2$  at 57nm (2008). A switch chip like the one presented will have an extrapolated area of 200  $mm^2$  at 130 nm, which becomes 110  $mm^2$  at 90 nm and 80  $mm^2$  at 80 nm technology, even reaching 50  $mm^2$  in the year 2008.

#### 1.4.2 On-Chip Memory

The switch chip designed for this work has a total of 1024 SRAM memories  $(32 \times 32)$ , one in each crosspoint. This large memory count, along with memory size (2KBytes), has been the main bottleneck in multi-port buffered crossbar switches, as it is an inherent characteristic of the buffered crossbar architecture. One technology that can overcome this limitation is Embedded DRAM (eDRAM). eDRAM offers many advantages, compared to conventional on-chip SRAM: (a) it is 1.5x to 4x denser[39], thus enabling smaller die sizes; (b) although active power is comparable for both types of memories, eDRAM draws orders of magnitude less standby current than a respective SRAM; (c) eDRAMs provide very wide I/O, although their random access times still lack those of conventional SRAMs (e.g. 90 nm fast eDRAMs can run at exess of 300 MHz[40, 41], whereas embedded SRAMs have already passed the 500 MHz "barrier"); (d) eDRAMs store larger amount of charge per cell than SRAMs, thus having minimal Soft-Error Rate per bit, whereas SRAMs need specific error checking and correction (ECC) hardware to overcome error limitations, with impacts on area and performance. One potential disadvantage is increased eDRAM cost[42], which is due to: (a) 20% increase to standard 6 Metal Layer process, due to increased mask number required (incremental processing cost); and (b) 5-10% cost increase, due to more complicated testing required. Nevertheless, incremental processing and test costs, like the ones mentioned, are offset by improved silicon yield, as eDRAMs are easily repaired when manufactured.

As a result, a 10 KByte eDRAM-per-crosspoint  $32 \times 32$  switch will be feasible in the very near future. Furthermore, taking into account that in the

$<sup>^{9}</sup>$ Note that advertisements may state that smaller technologies have been implemented in the laboratory, but it can take 2 to 3 years until the first companies reach actual production.

switch designed for this thesis, memory area accounted for approximately 70% of the total chip core area, the use of eDRAMs of the same size would lower chip size by approximately 50%, thus improving potential yield.

### 1.4.3 Chip/Wafer Sizes

Despite the tremendous technology improvements that will take place in the next 15 years, companies seem to have agreed on a standard upper wafer diameter limit of 300mm, which may grow to 450mm after nearly a decade. ASIC chip sizes also seem to limit themselves to  $570mm^2$ . Having the tremendous downsizing caused by transistor technology and a possible adoption of new memory architectures in mind, overall yield will certainly increase, thus making large crossbar switch chips even more feasible and cost-effective.

#### 1.4.4 Power Consumption

Power consumption is possibly becoming one of the most critical elements in hardware design today, as it can be the limiting factor of design performance. Projections show [36] [37] that in a few years: (a) power delivery and dissipation will be prohibitively high; (b) power density  $(W/cm^2)$  will grow to enormous figures <sup>10</sup>. This results in large power/ground wiring requirements, sets packaging limits, caused both by technology barriers, as well as cost<sup>11</sup>, and impacts on signal noise margins and reliability. As a result, power consumption must always remain as low possible, in order to avoid expensive packaging and cooling solutions.

<sup>&</sup>lt;sup>10</sup>Today, high-performance processors consume above 100 W (i.e., the 2 CPU, 2 MB L2 cache IBM Power4 consumes 115W in a  $3.8cm^2$  die) and have power densities near a nuclear reactor, increasing linearly every year.

$<sup>^{11}50</sup>W/cm^2$  for forced-air cooling and 120 W total power consumption; today's power-dependent pricing is about 1\$ per Watt.

# Chapter 2

# Switch Organization and Operation

### 2.1 Introduction

In this chapter we present the organization and operation of the  $32 \times 32$  crossbar switch. We decided to use 2 KBytes of memory per-crosspoint; this agrees with the results presented in [19] and translates into 1500 Bytes for a maximum packet size, plus 500 Byte times for the Round Trip Time; the latter corresponds to 400 nsec in 10 *Gbit/sec* link speeds, which is the line rate assumed both in [19] and in this work. The remainder of this chapter is as follows: first we present the switch "block-level" interface, determining the input/output signals needed and outlining the main functional blocks. Then we discuss switch internal block organization; we particularly describe the organization of the Crosspoint, Output Scheduler and Credit Scheduler sub-modules, followed by the enqueue logic, which we developed in order to test the operation of the switch.

### 2.2 Internal Architecture

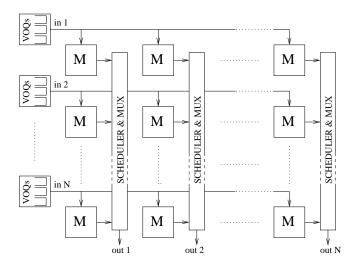

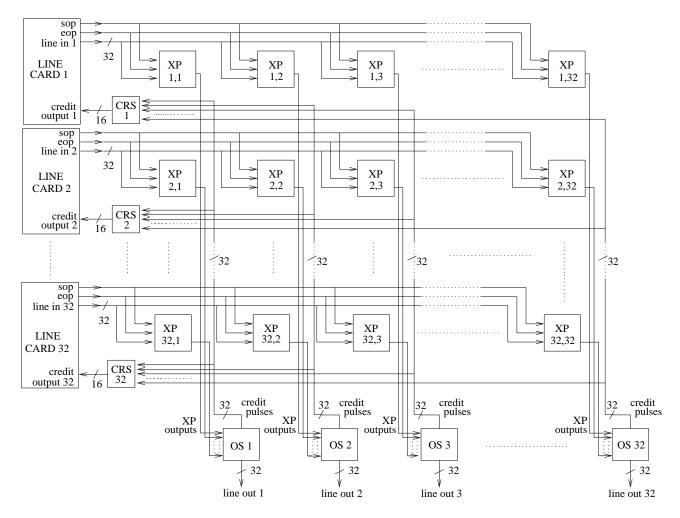

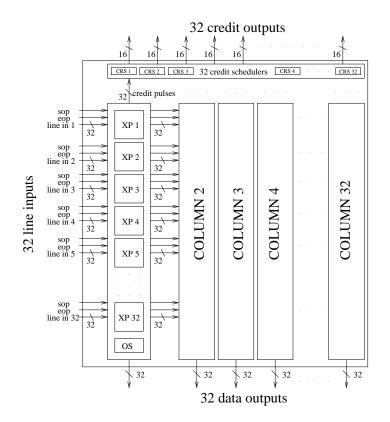

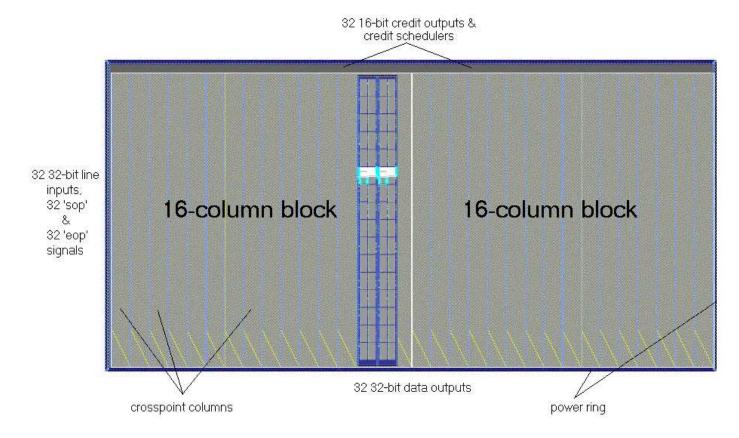

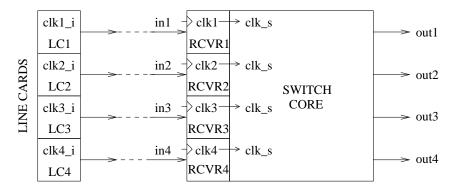

A top level block diagram of the switch can be seen in Figure 2.1. Switch interface has thirty-two 32-bit wide input data lines, 32 "Start Of Packet" and 32 "End Of Packet" input lines, thirty-two 32-bit wide data output lines and thirty-two 16-bit wide credit output lines. Apart from the obvious necessity of the data input and output lines, and the credit output lines, we also have to inform the switch that a new packet is about to be transmitted from the line cards to the fabric, as well as inform the fabric about the end of a packet transmission; this is accomplished by asserting the corresponding "Start Of Packet" (sop) or "End Of Packet" (eop) signal for one clock cycle.

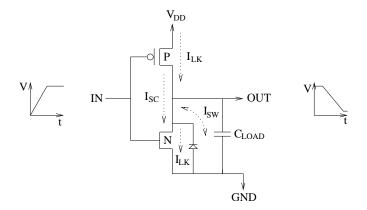

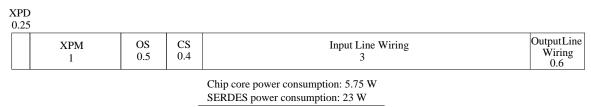

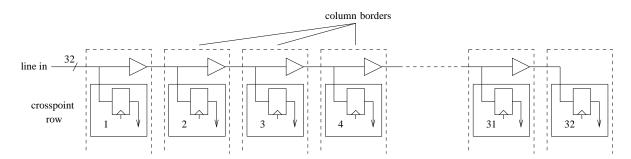

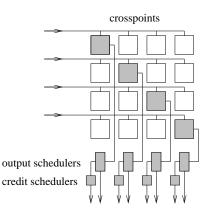

The switch core is divided into three parts: Crosspoint modules (XPs), Credit Schedulers (CSs) and Output Schedulers (OSs). Each crosspoint includes a  $512 \times 32$  (2 KB) SRAM, along with clock synchronization and mem-

Figure 2.1:  $32 \times 32$  crossbar switch block diagram: the switch consists of  $32 \times 32 = 1024$  crosspoints, and 32 output and credit schedulers. Line card logic is located outside the switch core.

ory enqueue/dequeue logic. A  $32 \times 32$  switch needs  $32 \times 32 = 1024$  XPs, thus 16 Mbits of memory. Credit Schedulers contain mechanisms for collecting and sending credit information to the input line cards, whereas Output Schedulers are responsible for selecting eligible flows that can send their packets to the chip outputs. Both the Credit and Output Schedulers implement the plain Round Robin discipline. Other scheduling disciplines, being fairer, could also be supported (i.e. [34]).

We place the clock domain boundaries in the crosspoint modules; thus, elastic buffers at the chip inputs are eliminated, which reduces latency and power consumption, as each word of packet payload is only written once into and read once out of a memory during its transition through the chip [19]. Note that the only control information that has to traverse two different clock domains in the switch organization presented, is the "new packet" arrival notification pulse. What is more, the two clock domains must operate in almost the same frequency, as the input and output links have the same speed. These observations significantly simplify crossbar design, as such 1-bit synchronization circuits are very simple and efficient.

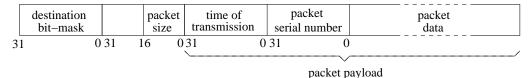

Before explaining the three main switch components in more detail, it should be noted that the switch supports directly TCP/IP packets, of sizes 40-1500 Bytes. Packet size must be a multiple of 4 and, if this is not the case, the input line cards have to fill the remaining bytes of the last word and accordingly increase the size of the packet. The only other information needed for the switch to operate is an output destination 32-bit multicast bitmask, which is sent just before the actual packet; this information is padded by the line card logic and the positions of the "1" indicate the crosspoints in which the packet is destined to or, equivalently, the outputs that the packet must be sent to. Destination bit-mask and packet size are accompanied by a "time of transmission" value and a "packet serial number" in the payload, both of which were added for debugging and statistic purposes (see Figure 2.2).

paenee paj ioaa

Figure 2.2: Supported packet format: apart from packet size (16 bits), a time of transmission (32 bits) and a packet serial number (32 bits) value was padded for statistic and debugging purposes. Packet payload follows. Notice the 32-bit mask added at the beginning of the packet.

#### 2.2.1 Crosspoint Blocks (Crosspoints)

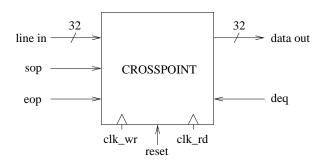

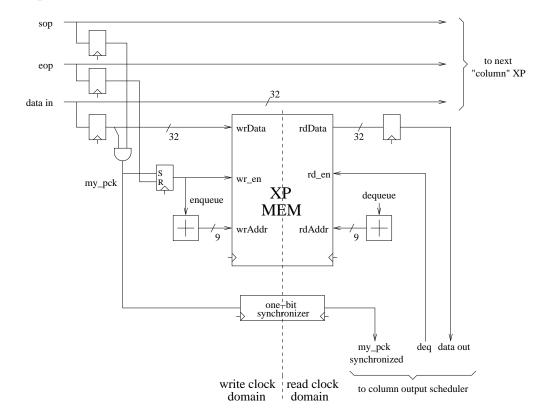

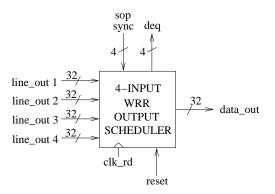

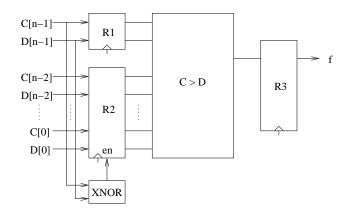

Crosspoints (XPs) are responsible for storing/retrieving packets into/from their corresponding buffer memories. Figure 2.3 shows the top-level block diagram of the crosspoint: a 32-bit wide packet data bus enters each crosspoint, along with the sop and eop signals. Each crosspoint receives a deq signal from the corresponding column output scheduler and sends to the output a 32-bit data\_out value. Notice the two different clock domains: the clock domain controlled by clk\_wr contains the writing circuits, while clk\_rd handles the data reads.

Crosspoint organization is shown in Figure 2.4. Each XP has a 32-bit wide input datapath, along with two control signals: a "Start Of Packet" (sop) signal, which must be asserted for one clock cycle during the transmission of the first packet word and an "End Of Packet" (eop) signal, which is asserted during the transmission of the last packet words. The sop signal informs XP logic that a new packet is being sent. Each crosspoint looks individually at a 32-bit destination bit-mask, described in the previous section,

Figure 2.3: Crosspoint block diagram.

and accordingly decides if the certain packet should be handled by it or not. The **eop** signal informs the crosspoint logic that the data enqueueing must stop.

Figure 2.4: Crosspoint organization: notice the two clock domains; they meet in the memory and in the 1-bit synchronizer circuit.

Both **sop** and **eop** signals are needed in order to reduce the complexity of the switch core. In fact, in order to remove those 64 signals, we would have to include some line-card and the packet enqueue control logic *inside* the switch, which would add to its area and complexity. On the other hand, if those logic blocks were placed inside the switch, credits would not have to be sent to the line cards, which would decrease the number of I/O ports needed. Although the last argument is very important in the case of medium- to large-scale buffered crossbars (as chip I/O throughput is limited and has to remain low for pin count, power consumption, and pricing reasons), a clever organization of credit logic can remove this initially predicted overhead  $^1$ .

In particular, in order to remove the **eop** signal, extra logic would have to be added inside the switch, which would detect the **sop** arrival, send the enqueue signal to the corresponding crosspoint, capture and decrement the packet's size, and deassert the enqueue signal when the packet is written. During most of the stages of this work, this logic was actually included in the switch, but its necessity proved worthless, as with just a little I/O throughput overhead <sup>2</sup>, this logic was easily omitted from the fabric. Note that only 32 such "enqueue logic" blocks were used, as we only needed one per switch row: every crosspoint that actually enqueued a packet would "listen" to the **eop** signal generated by that logic; the rest would just ignore it.

When both **sop** and the corresponding bit of the bit-mask are asserted, the crosspoint logic must perform a packet enqueue to the SRAM. This is carried out by setting a latched signal, called **my\_pck**, which in turn asserts the SRAM's write enable and increments the 9-bit enqueue address counter. When **eop** signal arrives, the enqueue FSM deasserts write enable and stops the enqueue pointer from incrementing.

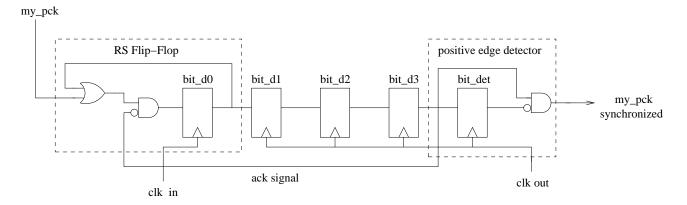

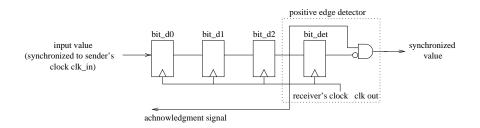

We must also forward the my\_pck signal to the corresponding output scheduler, informing that a packet is being enqueued to one of the 32 crosspoints connected to the column's scheduler. This event wakes up the output scheduler if the output link has been idle. We thus feed this new-packetarrival signal to a simple 1-bit synchronizer, which is depicted in Figure 2.5. The signal sets an RS flip-flop and its output Q is sampled by a series of three D flip-flops clocked by the output clock domain (clk\_rd). When the pulse is received, an acknowledgment signal travels back, which resets the RS flip-flop. The synchronization delay is 5 clock cycles, far less than the minimum packet size (40 Bytes) enqueue time, which, in the case of our 32-bit datapath, corresponds to 10 cycles. Note that the two clock frequencies are always close to each other, which is always the case in switches, since they have the same input and output throughput. Synchronizer design is briefly presented in the Appendix.

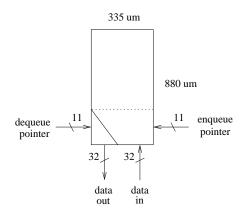

Packets are enqueued/dequeued in a  $512 \times 32$  (2 KByte) Two-Port Register File SRAM from Virtual Silicon Technology [43]. This memory has a 32-bit port for read and an independent 32-bit port for write; read and write addresses are 9 bits wide (see Figure 2.3). The independent read and write cycles are timed with respect to their own clocks, namely clk\_rd and clk\_wr respectively. It should be noted that during a read cycle, the output

<sup>&</sup>lt;sup>1</sup>This organization is thoroughly presented in a following section.

<sup>&</sup>lt;sup>2</sup>Not high chip I/O overhead, though, as "End Of Packet" transmission is carried out at most every "minimum-packet-size" time, which is 10 clock cycles in our 32-bit datapath; hence fast and expensive tranceivers are not needed.

Figure 2.5: 1-bit synchronizer circuit.

bus values are held if read enable is not asserted. This read enable feature is used to save RAM power without the need for external clock gating.

The last part of the crosspoint logic is the dequeue sub-module. Whenever the output scheduler decides to dequeue a packet from the specific crosspoint, it asserts the deq signal, which fires the dequeue FSM corresponding to that output; read enable is asserted and dequeue pointer is then incremented. The deq signal remains asserted for the time needed to fully dequeue the packet, and is controlled by the output scheduler dequeue logic.

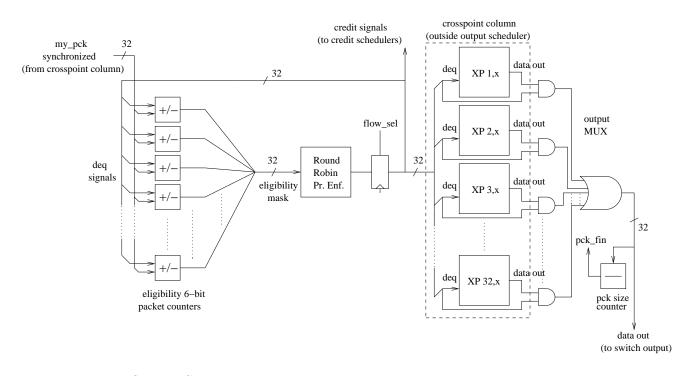

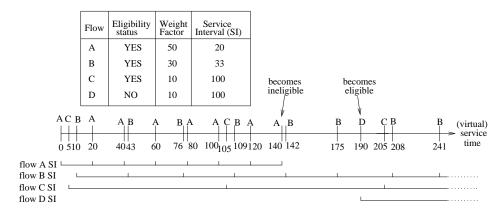

#### 2.2.2 Output Schedulers

The output schedulers are responsible for: (a) selecting the next eligible flow from a certain crosspoint of the same column; (b) initializing the transmission of packets to the specific switch output; and (c) sending a credit back to the line cards. A flow is called *eligible* if the corresponding crosspoint contains packets that are waiting to be sent. If there are more than one eligible flows, the output scheduler has to select one of them; this selection can depend on the flow priority (possibly its *weight* - i.e. in Weighted Round Robin scheduling), or on a plain round robin policy. In this work we did not aim at implementing new and sophisticated output scheduler policies, but rather use a plain round robin scheduler: the output scheduler maintains a list of the eligible flows and after serving one flow, it selects the next eligible flow of the list <sup>3</sup>. The output scheduler knows which flows are eligible or not through the synchronized my\_pck signals it receives from the crosspoints of the same column. Since the synchronization delay is 5 clock cycles and a packet transmission lasts for 10 cycles, we claim that the scheduler supports *cut-through* operation (with a 5 cycle overhead): when all 32 crosspoints

<sup>&</sup>lt;sup>3</sup>In the first stages of this thesis, we developed a Weighted Round Robin output scheduler with "smart comparator usage" for a  $4 \times 4$  crossbar switch, that would be implemented in an FPGA. This scheduler is examined in the Appendix.

of a column are empty and a minimum-size packet arrives to one of them, only 5 clock cycles are needed to initialize its dequeue to the switch output, whereas the time needed for the packet to be written to the crosspoint is 10 clock cycles.

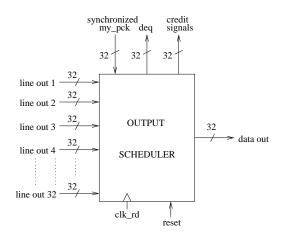

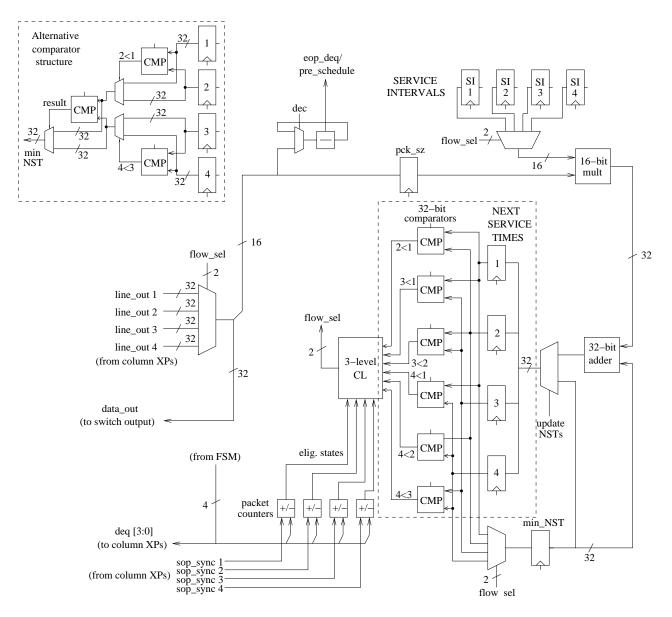

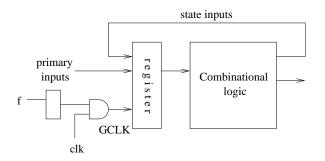

Output scheduler block diagram can be seen in Figure 2.6, while its organization is presented in Figure 2.7. The scheduler has thirty-two 32-bit data

Figure 2.6: RR Output Scheduler block diagram.

inputs, which originate from the column crosspoint memories' data outputs. 32 synchronized my\_pck signals are also sent from the crosspoint synchronization logic. The output scheduler sends 32 credit signals back to the switch inputs and a 32-bit deq bus to the column crosspoints. The dequeue signals act as read enable for the crosspoint memories.

In order to produce the list of eligible flows, the scheduler maintains thirty-two 6-bit packet counters <sup>4</sup>, which are incremented each time a synchronized  $my_pck$  signal arrives and decremented when the selected packet is being dequeued; when these counters are equal to zero, the flow is ineligible. The 32-bit eligibility mask that is created in this way enters a Round-Robin Priority Enforcer, which is responsible for selecting the next eligible flow (its output is a 32-bit value, with one bit equal to "1" and 31 bits equal to zero). This 32-bit crosspoint selection bus is sent to the column crosspoints and at the same time the specific packet counter value is decremented. When the first packet word is dequeued from the crosspoint and arrives at the scheduler, the packet size is stored, in order to allow the scheduler to know when it should stop dequeueing. If, while one packet has been almost dequeued, there exists at least one eligible flow in the same column, the scheduler has to start *pre-scheduling*, in order to choose the next eligible flow and not miss any clock cycles in between. Hence, back-to-back operation is achieved.

<sup>&</sup>lt;sup>4</sup>Six bits are sufficient because each crosspoint buffer can store at most 50 (minimumsize) packets.

Figure 2.7: RR Output Scheduler organization: crosspoint memories are illustrated for clarity; they do not belong to the output scheduler.

#### 2.2.3 Credit Schedulers

Credit schedulers are responsible for: (a) collecting the credit signals from the output schedulers; and (b) sending them back to the line cards; there is one line card per row. Since it is the line cards' responsibility to recover the receiving clock (as happens with outgoing packet data), credits are sent in respect to the output clock, hence no synchronization circuitry is required.

The credit format should satisfy one constraint: it should contain the absolutely necessary information that the line card should know, in order to save I/O bandwidth (package pins and expensive I/O pads). In order to remove as much logic possible from the switch core, we decided that the line cards should perform all necessary credit computing operations. For error resilience purposes, the credit schedulers adopt a QFC-like [30] approach: instead of sending the information that "the next packet has just left from crosspoint ..." <sup>5</sup>, they just send "the total, cumulative number of packets that have left up to now from crosspoint ..., modulo  $2^k$ , is equal to ..." [19]. As a result: (i) we do not need to send one credit for every packet; and (ii) even if some credits get lost, the next arriving credit carries cumulative information from past ones, too <sup>6</sup>. Line card logic is responsible for concluding

<sup>&</sup>lt;sup>5</sup>This information could have the form of a 5-bit encoded crosspoint (i.e. output) number, but one such credit loss would have undesirable effects.

<sup>&</sup>lt;sup>6</sup>We just have to ensure that at least one credit will safely arrive for every  $2^k$  departing

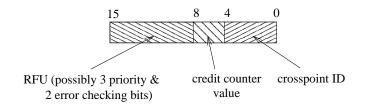

that the credit number just received is different from the previously stored corresponding value, hence a new credit has arrived. Credit format is shown in figure 2.8. It is 16 bits wide, with the most significant 7 bits reserved for future use (possibly 2 bits for error checking purposes, plus 3 bits for supporting up to 8 distinct priorities). The next 4 bits contain the actual credit value (number of packets sent from the corresponding crosspoint), while the 5 least significant bits refer to the crosspoint's ID.

Figure 2.8: Credit format.

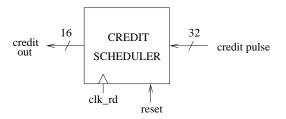

Figure 2.9 shows the credit scheduler block diagram. Each credit scheduler module receives a 32-bit credit mask, referring to dequeues from the corresponding row crosspoints, and sends a 16-bit credit bus to the respective line card logic.

Figure 2.9: RR Credit Scheduler block diagram.

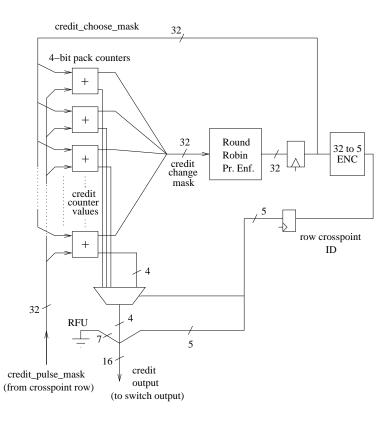

Credit scheduler internal organization is shown in Figure 2.10. The scheduler maintains 32 4-bit "sent-packet" counters, which contain the number of packets that have been dequeued from the respective row crosspoints. Obviously this counter wraps around when 16 packets have been dequeued and the 17-nth credit has just arrived.

Each time a credit arrives, the respective credit counter sets its output credit\_change bit, informing the scheduler that its value has just changed. The 32-bit credit\_change\_mask value is connected to a Round Robin Priority Enforcer, which selects the next (changed) credit value that will be sent to the line cards. This is indicated by its 32-bit output, credit\_choose\_mask, which, except for selecting the credit value that will be sent to the line cards, is also responsible for *resetting* the credit\_change flag of the corresponding counter.

packets, i.e. before the counter wraps around.

Figure 2.10: RR Credit Scheduler organization.

Assuming that credit switch outputs will use about 1/8 of the bandwidth of every switch packet data input/output<sup>7</sup>, each 16-bit credit value will need 4 clock cycles in order to be sent to the line card<sup>8</sup>. As a result, scheduling is carried out in 4-cycle intervals. Since scheduling time is 4 clock cycles, the scheduler needs  $4 \times 32 = 128$  clock cycles to send all 32 credit values.

Credit signals can arrive at any time from the output schedulers, with the extreme of all 32 bits of the credit\_pulse\_mask being set in one clock cycle. In this case, credit\_change\_mask is all "1" and one credit counter value is selected to be sent. Due to the fact that the next credit signals will come *at least* one minimum-packet transmission time after this event (10 clock cycles), no counter can overflow sooner than 170 clock cycles have passed; hence, the scheduler has enough time to send all 32 credits before any counter wraps around.

Last of all, it should be noted that if the credit\_change\_mask is all zeroes, meaning that no credit has been received for at least the last 128 clock cycles (nearly 13 packet-times), the credit scheduler sends the stored credit counter values. In this way, the line card logic can check if the credit

<sup>&</sup>lt;sup>7</sup>This is desirable in order to save package pins and I/O tranceiver pads.

$<sup>^{8}</sup>$ In one cycle, 32 packet data bits are received/sent, hence if credits use 1/8 of this bandwidth (4 bits per cycle), 4 cycles are needed for the transmission of the 16-bit credit value.

value has changed since last time and thus perform error checking.

#### 2.2.4 Line Card Logic

The switch presented sofar could be tested in two ways: (a) by feeding the simulator with trace files containing real or generated traffic; and/or (b) by designing a simple line card and feeding the switch with traffic from the line card's traffic generator. During the initial stages of the switch design, we used traces generated from the simulator which was written in C++ and is thoroughly presented in [29] and [19]. The trace files consisted of packet sizes and the exact time they were arriving at the switch inputs. Later on, the credit logic designed in the simulator changed from the one we used and, as a result, in order to test and verify the switch operation, we designed a Verilog model of the line card.

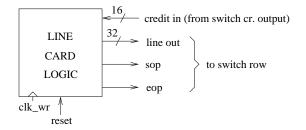

Line card block diagram is presented in Figure 2.11. Each line card is

Figure 2.11: Line Card block diagram

responsible for sending packet data (32-bit line out bus), and the "Start Of Packet" (sop) and "End Of Packet" (eop) signals to the respective switch row. Feedback information from the switch is packed in the 16-bit credit bus that is sent through the corresponding switch credit scheduler to the line card block. Line card constists of two parts: (a) packet construction and transmission logic; and (b) credit processing logic. These two parts are completely independent, as a credit can come at any time, regardless of the state of a possible packet transmission. The two parts are discussed in more detail in the next two subsections.

#### Packet Construction and Transmission Logic

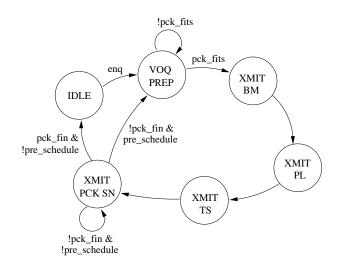

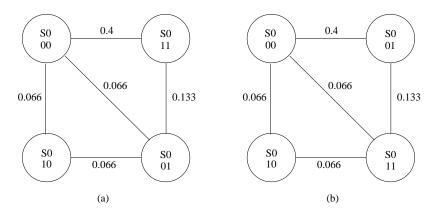

As each line card has multiple (32) Virtual Output Queues (VOQs), 32 FIFO queues are maintained; these contain the size of each packet that has just begun transmission from the line card to the switch. A 32-entry "empty crosspoint buffer size" array is also used, in order to store the empty space of each crosspoint buffer of the corresponding switch row. The packet transmission FSM is shown in Figure 2.12. This FSM is in the IDLE state if no packet can/has to be constructed and sent. When the enq signal is set, the

Figure 2.12: Line card packet transmission FSM.

FSM goes to VOQ\_PREP state. If the new packet's size fits into the corresponding crosspoint buffer, pck\_fits is asserted, packet size is enqueued in the respective FIFO, the specific crosspoint buffer size is decremented by the pck\_sz value and the corresponding packet counter is incremented. The next four states are responsible for sending to the switch the packet bit mask (XMIT\_BM), packet length (XMIT\_PL), a timestamp (XMIT\_TS) and the packet's serial number (XMIT\_PCK\_SN); packet format is shown in section 2.2. In order to support back-to-back transmission (pre\_schedule is asserted), the FSM goes to the VOQ\_PREP state before the packet's last word is sent to the switch, and the preperations for a new packet transmission start.

#### Credit Processing Logic

In this behavioral module, a 32-entry credit array is maintained in order to store the previous credit counter values. These values are compared with the newly received ones: if they differ, then we have a new credit for that particular VOQ. As a result, a FIFO dequeue has to be performed, the new credit value must be stored and the empty space of that particular crosspoint has to be incremented by the packet size stored in the head of the FIFO.

#### Switch Verification

The switch is tested by using the Cadence [20] NCLaunch tool. Three types of traffic are sent: (a) all minimum-size packets (40 Bytes); (b) randomly selected packets; and (c) only maximum-size packets (1500 Bytes). Packets are sent either back-to-back, or with a random interpacket delay. We use two test scenarios: (a) all inputs send packets to all outputs randomly; (b) all inputs send packets to a specific output; obviously, the scenario that puts more stress on the switch core is when smallest size packets are sent backto-back to a specific output. In that case, the crosspoint buffers of that switch "column" are filled with 40-Byte packets and the output scheduler has to make a decision in 10 clock cycles, which is the transmission time of a minimum-size packet. In this way, we achieve back-to-back operation.

### 2.3 Conclusions

In this chapter we presented in detail the switch and line card internal organization and operation. Crosspoint logic should be as small as possible, as the  $O(N^2)$  crossbar complexity could prove, in the later design stages (synthesis and placement & routing), to be a prohibitive implementation factor. By minimizing the logic at the clock domain boundaries, synchronization becomes easy and simple. Furthermore, no packet segmentation and reassembly is required, by directly supporting variable-size operation and with padding a 32-bit destination bit-mask at the beginning of each packet header. Output and credit schedulers are as simple as possible, whereas their aggregate size is orders of magnitude smaller than total memory area; hence, more complex policies can also be supported, without significantly affecting the total switch core area.

# Chapter 3

# Logic Synthesis

### 3.1 Introduction

Logic synthesis is one of the most important phases of the design flow in stateof-the-art circuits. It aims at transforming the HDL (usually Verilog HDL or VHDL) description of the circuit into a technology-dependent, Gate-Level netlist. Through this process, the hardware designer defines the environmental conditions, contraints, compile methodology, design rules and target libraries, in order to achieve certain design goals set by the initial specifications. The Gate-Level representation of the circuit is the input file to the Place & Route tool, which is described in the next chapter.

The tool we use for the logic synthesis of the switch is Synopsys Design Compiler (DC) [46], the most widely used synthesis tool. Design Compiler optimizes logic designs for speed, area and wire routability. From the defined goals, DC synthesizes the circuit and tailors it to a target technology. The rest of this chapter is as follows: first we present the two ways the synthesis procedure can be carried out, flat and hierarchical, and compare them. We then describe the synthesis flow we followed for the  $32 \times 32$  buffered crossbar switch, accompanied by our synthesis results. Later on, we will compare these results to the placement & routing ones and useful conclusions will be drawn. Finally, we briefly talk about post-synthesis verification.

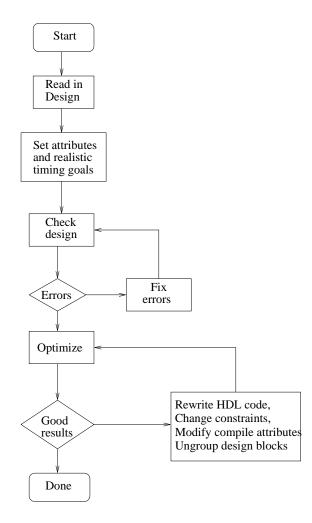

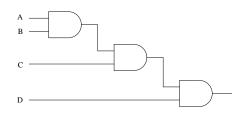

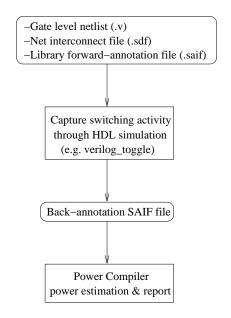

## 3.2 Synthesis Flow

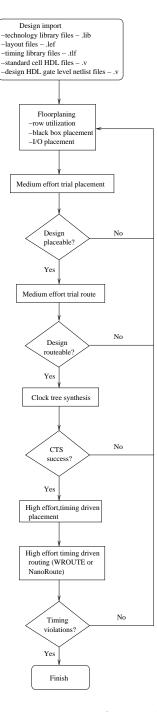

The synthesis flow that we follow can be seen in Figure 3.1. We initially *read* the design under synthesis; this enables DC to load all design instances into memory and report possible HDL errors. Next we *set initial design constraints*, such as: (a) maximum circuit area, or zero if ultra "size" minimization has to be performed; (b) circuit clock(s); (c) maximum transition time of specific nets; (d) maximum capacitance of nets, etc. Circuit area and clock cycle specification are usually enough in order to synthesize most circuits. Design must then be *checked*. This enables Synopsys to report mis-

takes which usually have to do with wrong module instantiations, or interface mismatches. After this "check design" phase is complete, we optimize the design, by setting again the appropriate values for the different constraints. Usually, we wish to minimize circuit area and increase operating frequency. Some nets may also have to be constrained in terms of capacitance or timing, but these decisions can usually only be taken into account after actual chip layout is defined. As a result, the latter has to be almost defined before synthesis commences. After this final phase, we analyse the reports of the tool and check for unmet constraints. If such exist, the designer usually has to: (a) rewrite HDL code, in order, for example, to meet certain timing constraints; (b) modify the constraints themselves, which unfortunately may result in a slightly different design; (c) change compile attributes, for example, change tool optimization priorities; (d) ungroup (i.e. remove any hierarchy from design blocks), in order to offer the tool the ability to handle larger modules and possibly produce better analysis and optimization results; unfortunately, we cannot completely remove the hierarchy in the case of very large designs. Last of all, we can analyze power consumption and perform power optimizations. Synthesis power estimation is presented in chapter 5, while power optimization techniques can be found in the Appendix.

## **3.3** Flat vs. Hierarchical Synthesis

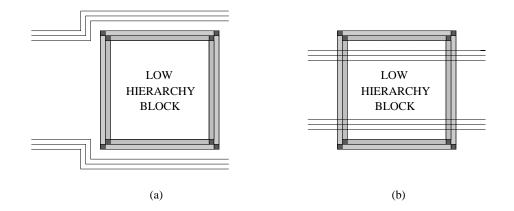

Flat designs contain no subdesigns and have only one structural level; they only contain library cells. Design Compiler does not optimize across hierarchical boundaries; therefore, by removing the hierarchy within certain designs, timing results can be improved. Removing of hierarchy is called ungrouping. Through this task, subdesigns of a given level of hierarchy are merged into the parent design.

Although flat synthesis usually provides the best results, this approach cannot be followed in the case of large designs. This is because, at the presence of a large number of multi-instantiated modules, ungrouping will build every instantiated module from scratch, thus needing large computational resources. In such cases, a hierarchical approach is proposed: each module is synthesized, fully optimized, and saved as a separate design. Then, it is loaded back to the tool and linked into the higher hierarchy module. Synopsys will then only have to deal with identicaly-synthesized module instantiations, which will reduce execution time. One disadvantage of the hierarchical approach is that the tool cannot perform low-level optimizations, after the higher-level design is synthesized. Such optimizations are useful when, for example, the designer wishes to optimize the design for power consumption. In that case, cells that are located at non-critical paths are usually replaced by others that are smaller, hence consume less power, but are slower. Such optimizations cannot be performed inside low-hierarchy blocks directly at the top-level of a hierarchical design.

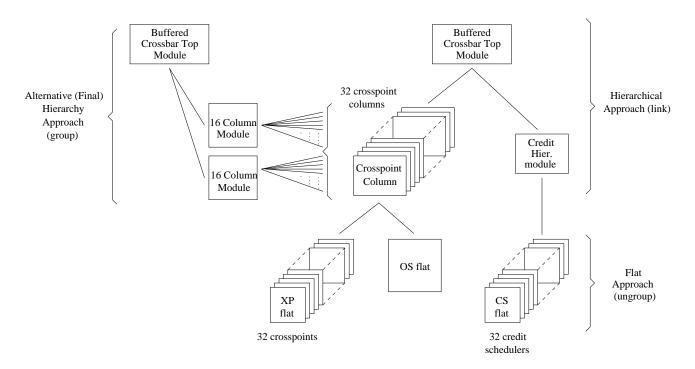

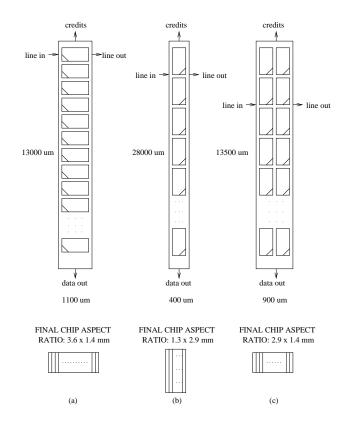

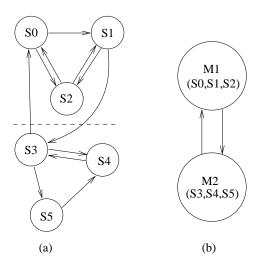

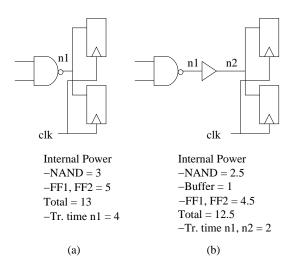

Figure 3.1: Generic synthesis flow.

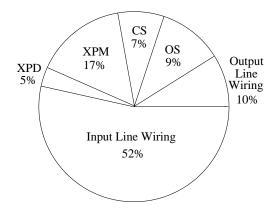

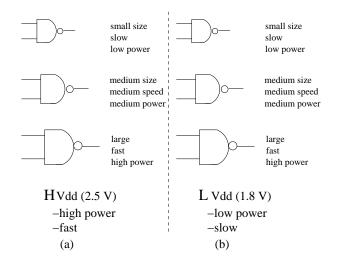

Synthesis hierarchy organization followed can be seen in Figure 3.2. We synthesize low hierarchy blocks, like crosspoints, output and credit schedulers in a flat manner. This is decided in order to achieve maximum optimization on those blocks; the latter is required because, due to the large instantiation number of these blocks (1024 crosspoint and 32 output and credit scheduler modules), lack of optimization can eventually limit the design goals. These low hierarchy blocks are then grouped into higher hierarchy modules: 32 columns include 32 crosspoints and one output scheduler module each, whereas one credit module is used to group the 32 credit schedulers. These groupings are performed in the RTL, but can also be carried out successfully through the Synopsys environment, by using the group command. As a result, the top design module consists of merely 32 column and one credit module.